Samtec loves DesignCon. It’s an opportunity to present our new signal integrity optimized, high-performance interconnect and technology solutions, along with the highest level of support and expertise in the industry.

To learn more about these products and solutions, stop by the Samtec Booth, #737. I’m trying to be objective here, but if you’re in California the last week of January (or if you’re in any of the other 50 states (or Canada or Mexico)), you need to stop by booth #737 at DesignCon 20. That’s the Samtec booth, which will be the coolest booth in the history of all electronics tradeshows ever.

Sorry, I got carried away. I should be more humble and say it’s the coolest booth in all of electronics for the last 50 years. It’s ridiculous to say it’s the coolest ever. Anyway, here’s a list of Samtec in-booth demonstrations, presentations, papers, and panel discussions:

DEMONSTRATIONS

Swing by DesignCon booth 737 (that’s the Samtec booth) any time to see these demos that use real-world signal integrity design practices:

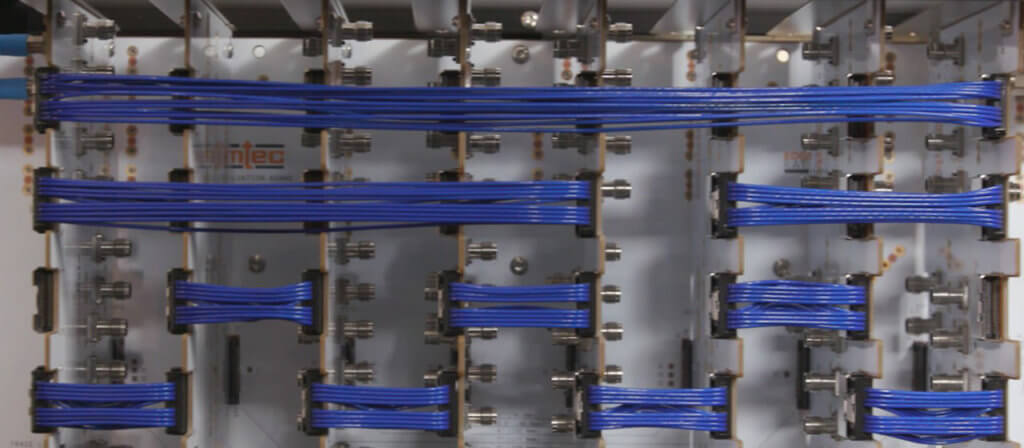

112 Gbps PAM4 Front-Panel to Mid-Board Flyover® Technology: This collaboration between Samtec and Alphawave emulates next generation data center equipment architectures. It incorporates Samtec Flyover to improve signal integrity and architectural flexibility. Samtec Flyover routes critical high-speed signals from the ASIC, above lossy PCB materials, directly to the panel, utilizing ultra-low-skew twinax cable. (There’s an in-booth presentation on Thursday, January 30, at 12:00 pm)

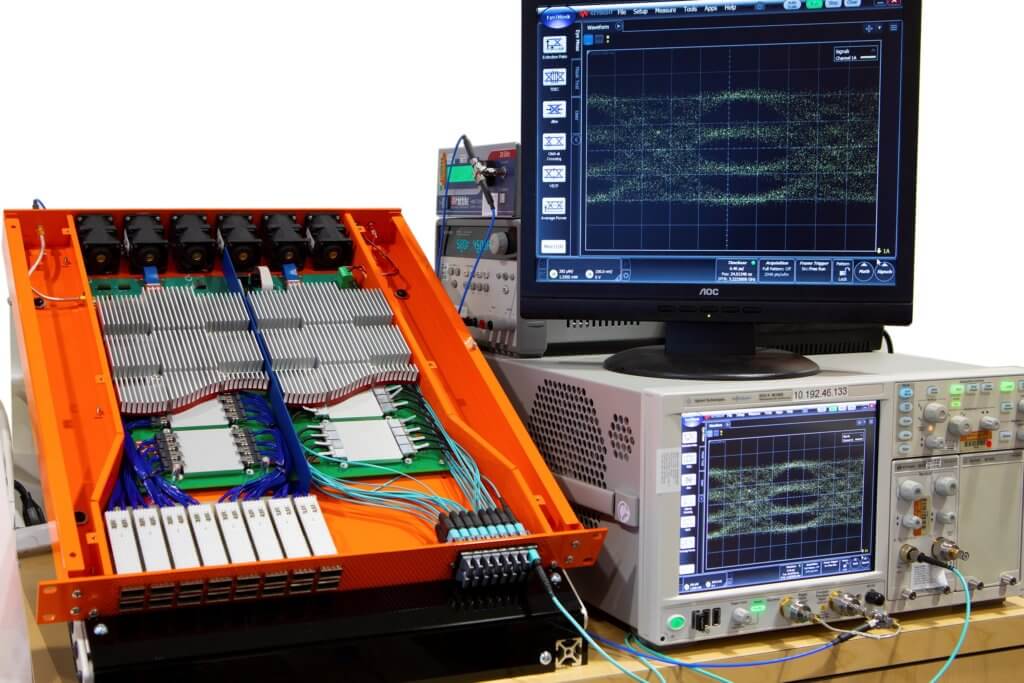

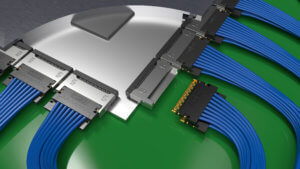

112 Gbps PAM4 Mid-Board to Cabled Backplane Flyover® Technology: Samtec’s NovaRay™ extreme density array, combined with ExaMAX® backplane cable assemblies, retains a traditional backplane architecture, but with higher performance targets and lower PCB complexity. This demo features a Xilinx 112 Gbps PAM4 7nm test chip running multiple 112 Gbps PAM4 XCVRs. (In-booth presentation Thursday, January 30, 2:00 pm)

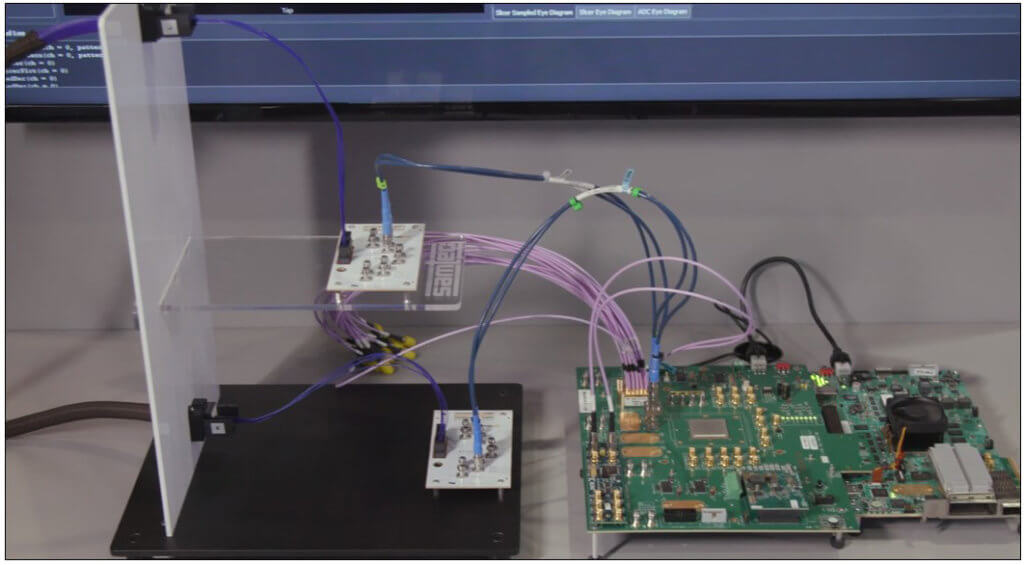

Direct Connect™ To Silicon Package: This demonstration highlights Samtec Direct Connect technology, which eliminates distortion through the BGA region by directly connecting to the silicon package. Optical and copper FireFly™ Micro Flyover System™ cable assemblies connect eight BGA-style packages to the front panel and backplane, enabling up to 56 Gbps PAM4 at a pJ/bit that is three times more efficient than QSFP25. (In-booth presentation Wednesday, January 29, 5:00 pm)

High Performance Test Solutions: This in-booth demonstration of a 70 GHz capable test platform features Samtec Bulls Eye® high-performance test point system and Credo Bald Eagle II Retimer. (In-booth presentation Wednesday, January 29, 12:00 pm)

Scalable 32 GT/s Silicon Test Platform For AI: Leveraging the GenZ™ PECFF, Samtec and Synopsis demonstrate PCIe® GEN 5 performance over a cable mesh backplane and edge card connectors in a configurable and scalable system architecture targeting AI applications. (In-booth presentation Thursday, January 30, 5:00 pm)

FEATURED PRODUCTS:

Here’s a list of some of the new and newer products that will be on display in Samtec’s DesignCon booth. Did I mention we’re in booth #737?

NovaRay™ Extreme Density Arrays: The innovative design of NovaRay combines extreme density and performance, which is critical as system sizes decrease and speeds increase. The fully shielded differential pair design and two reliable points of contact contribute to the industry leading 4.0 Tbps aggregate data rate.

ExaMAX® Backplane Systems: This backplane system improves signal integrity and routability using Samtec Flyover technology. ExaMAX products are available for traditional backplane, cable-to-board, cable-to-cable, mid-board, and panel applications.

Bulls Eye Test Point System: The high-density array designs and advanced cabling solutions within Samtec’s Bulls Eye product family enable optimized performance, now to 70 GHz. Compression interface, small footprint and high cycle count make Bulls Eye ideal for high-performance test applications.

FireFly™: FireFly™ Micro Flyover System™ is the first interconnect system that gives a designer the flexibility of using micro footprint high-performance optical and low-cost copper interconnects interchangeably with the same connector system.

Si-Fly™: The ultra-high density design and on-package direct connect technology of this cable system enables speeds of 25.6 TB aggregate, with a path to 51.2 TB.

Flyover QSFP-DD: This double density QSFP28 cable system utilizes Samtec Flyover.

AcceleRate®: AcceleRate® is the industry’s slimmest cable system with direct attach technology and ultra-low skew twinax cable for 56 Gbps PAM4 speeds.

PRESENTATIONS WITH PARTNERS

- TOPIC: Optimizing 112 Gbps PAM4 Interconnect Design Leveraging ANSYS® HFSS™

- DESCRIPTION: Scott McMorrow will detail Samtec’s 112 Gbps PAM4 interconnect design process that leverages the multi-physics modeling and simulation capabilities of ANSYS® HFSS™.

- WHERE AND WHEN: Wednesday, January 29th / 1:00 pm / Ansys Booth #745

- TOPIC: Correlating Data at 112 Gbps PAM4/53 GHz

- DESCRIPTION: Samtec’s Scott McMorrow and Keysight’s Mike Resso highlight the technical challenges or correlating simulated and measured performance data at 112 Gbps PAM4 /53 GHz via Keysight’s PXI VNAs and PLTS.

- WHERE AND WHEN: Wednesday, January 29th / 3:00 pm / Keysight Booth #725

PRESENTATIONS, PAPERS, and PANELS

Samtec associates are presenting, discussing, and paneling all over the place at DesignCon:

- PANEL: Stump the SI/PI Experts

- WHERE AND WHEN: Wednesday, January 29 / 11:15 am / Chiphead Theater

- DESCRIPTION: You guessed it, a panel of SI experts welcomes your questions.

- PAPER: Finding Reflective Insertion Loss Noise and Reflectionless Insertion Loss

- WHERE AND WHEN: Wednesday, January 29 / 2:00 pm / Ballroom D

- DESCRIPTION: This paper identifies the pitfalls of the insertion loss deviation which utilizes a fitted attenuation profile and is not able to distinguish between the reflections and coupling to resonant structures.

- PAPER: Current Distribution, Resistance & Inductance in Power Connectors

- WHERE AND WHEN: Wednesday, January 29 / 2:50 pm / Ballroom G

- DESCRIPTION: This paper analyzes the frequency dependent resistance and inductance of power connector pin patterns.

- PANEL: Next Gen Materials For High-Speed Digital Design

- WHERE AND WHEN: Wednesday, January 29 / 3:45 pm / Ballroom G

- DESCRIPTION: The objective of this panel session is to discuss the need for glass-reinforced or PTFE dielectrics that can support the needs of 28, 56, 112, or 128 Gbps, along with developing a system for winnowing the list of laminate possibilities from different laminate vendors—or within the same vendor once you’ve chosen a laminate.

- PRESENTATION: Validation of Achieving 100 Gbps Signaling per Electrical Lane Over 2 Meters of Passive Twin Axial Copper Cable

- WHERE AND WHEN: Thursday, January 30 / 8:00 am / Ballroom D

- DESCRIPTION: The IEEE 802.3ck Task Force is developing physical layer (PHY) specifications for operating speeds of 100 Gb/s, 200 Gb/s and 400 Gb/s based on 100 Gb/s signaling per electrical lane. Developing test and validation processes and philosophies often incur questions which may not be immediately evident on reading the specification; the paper is to assist with that understanding.

- PANEL: PCIe 32 G and 64 G: System Design and Test Challenges

- WHERE AND WHEN: Thursday, January 30 / 3:45 pm / Ballroom F

- DESCRIPTION: As PCI Express 5.0 system development commences, 64G-PAM4 has been announced to follow in 2 years. Join our panel to discuss the challenges in PCIe 5.0\6.0 system designs and validation.

- PANEL: How To Become An Industry Influencer

- WHERE AND WHEN: Thursday, January 30 / 4:15 pm / Chiphead Theater

Here’s a link to a complete list of all Samtec DesignCon activities.

Oh yeah, we’re in booth #737.

Leave a Reply