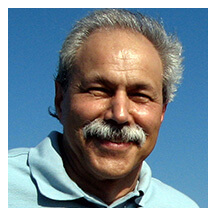

Samtec’s Istvan Novak has been named DesignCon Engineer of the Year. Congratulations, Istvan!

Istvan is a Principle Signal and Power Integrity Engineer at Samtec, working on advanced signal and power integrity designs. He introduced the industry’s first 25 um power-ground laminates for large rigid computer boards and worked with component vendors to create a series of low-inductance and controlled-ESR bypass capacitors.

DesignCon 2020 Best Paper Award

Samtec proudly congratulates several of our SI/PI technical experts for winning a DesignCon 2020 Best Paper Award. This year, Samtec technical experts Adam Gregory, Clement Luk, Gary Biddle, Gustavo Blando and Istvan Novak were awarded in the Power & RF section. Their paper was titled “Current Distribution, Resistance & Inductance in Power Connectors.”

DesignCon Best Paper Awards are chosen based on feedback from the DesignCon Technical Program Committee and event attendees. Winners are chosen based on technical merit and presentation ability.

Click here to view Paper.

Click here to view Presentation.

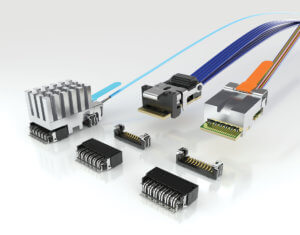

Samtec is prepared for the fast approaching technical renaissance with innovative Silicon-to-Silicon solutions that exceed standard connectivity demands. New architectures will require massive increases in transmission speeds, bandwidths, frequencies and densities. Samtec is addressing these challenges with a broad line of signal integrity optimized, high-performance interconnect and technology solutions, along with the highest level of expertise in the industry.

Below are the details from our demonstrations and presentations at DesignCon 2020.

Featured Demos – Samtec Booth 737

High-Performance Test Solutions Up To 70 GHz

In-booth demonstration of a 70 GHz capable test platform featuring Samtec’s Bulls Eye® High-Performance Test System and Credo Bald Eagle II Retimer.

Click here to watch the demonstration.

Direct Connect™ to Silicon Package

The demonstration highlights Samtec Direct Connect™ technology, which eliminates distortion through the BGA region by directly connecting high-speed signals to the silicon package. Optical and Twinax Flyover® cable assemblies connect eight BGA-style packages to the front panel and backplane enabling up to 56 Gbps PAM4 at a pJ/bit, the architecture of a 12.8 Tb system in a 1U chassis.

Click here to watch the demonstration.

112 Gbps PAM4 Front-panel to Mid-board Flyover® Technology

Samtec and Alphawave will emulate common data center architectures routing multiple 112 Gbps PAM4 data paths from the front-panel to mid-board, ASIC-adjacent topology.

Click here to watch the demonstration.

112 Gbps PAM4 Mid-board to Cabled Backplane Flyover® Technology

In-booth demonstration of 4x data paths between multiple 112 Gbps PAM4 SerDes through via two NovaRay® Cable Assemblies and a long-reach ExaMAX® Backplane Cable Assembly.

Click here to watch the demonstration.

Scalable 32 GT/s Silicon Test Platform for AI

Leveraging the Gen-Z™ PECFF form factor, Samtec and Synopsys will demonstrate PCIe® Gen 5 performance over a cable mesh backplane and card edge connectors in a configurable and scalable system architecture targeting AI applications.

Partner Presentations

Wednesday, January 29th | 1:00 pm

Optimizing 112 Gbps PAM4 Interconnect Design Leveraging ANSYS® HFSS™ – Ansys Booth 745

Scott McMorrow will detail Samtec’s 112 Gbps PAM4 interconnect design process that leverages the multi-physics modeling and simulation capabilities of ANSYS® HFSS™.

Click here to watch the demonstration.

Wednesday, January 29th | 3:00 pm

Correlating Data at 112 Gbps PAM4/53 GHz – Keysight Booth 725

Samtec’s Scott McMorrow and Keysight’s Mike Resso highlight the technical challenges or correlating simulated and measured performance data at 112 Gbps PAM4 /53 GHz via Keysight’s PXI VNAs and PLTS.

Technical Presentations & Panel Discussions

Wednesday, January 29th | 11:15 am

Panel – Stump the SI/PI Experts

Presenters: Istvan Novak, Eric Bogatin, Larry Smith, Vladimir Dmitriev Zdorov, Steve Sandler

Room: Chiphead Theater

Track Name: Chiphead Theater Discussion

Wednesday, January 29th | 2:00 pm

Finding Reflective Insertion Loss Noise and Reflectionless Insertion Loss

Click here to view Paper.

Click here to view Presentation.

Presenters: Hansel Dsilva, Sasikala J, Abhishek Jain, Amit Kumar, Richard Mellitz, Adam Gregory, Beomtaek Lee

Room: Ballroom D

Track Name: 07 Optimizing High-Speed Serial Design, 13 Modeling & Analysis of Interconnects

Description: This paper identifies the pitfalls of the insertion loss deviation which utilizes a fitted attenuation profile and is not able to distinguish between the reflections and coupling to resonant structures.

Wednesday, January 29th | 2:50 pm

Current Distribution, Resistance & Inductance in Power Connectors

DesignCon 2020 Best Paper Award

Click here to view Paper.

Click here to view Presentation.

Presenters: Adam Gregory, Istvan Novak, Clement Luk, Gustavo Blando

Room: Ballroom G

Track Name: 10 Power Integrity in Power Distribution Networks, 13 Modeling & Analysis of Interconnects

Description: This paper will analyze the frequency dependent resistance and inductance of power connector pin patterns.

Wednesday, January 29th | 3:45 pm

Panel – Next Gen Materials for High-Speed Digital Design

Presenters: Bill Hargin, Don DeGroot, Allen Horn, Scott McMorrow, Edward Kelley, Antonio Senese

Room: Ballroom G

Track Name: 04 Advances in Materials & Processing for PCBs, Modules & Packages, 07 Optimizing High-Speed Serial Design

Description: The objective of this panel session is to discuss the need for glass-reinforced or PTFE dielectrics that can support the needs of 28, 56, 112, or 128 Gbps, along with developing a system for winnowing the list of laminate possibilities from different laminate vendors—or within the same vendor once you’ve chosen a laminate.

Thursday, January 30th | 8:00 am

Validation of Achieving 100-Gbps Signaling per Electrical Lane Over 2 Meters of Passive Twin Axial Copper Cable

Click here to view Paper.

Presenters: CHRISTOPHER DIMINICO, Richard Mellitz, OJ Danzy, Michael Resso, Mike Sapozhnikov, Michael Klempa

Room: Ballroom D

Track Name: 13 Modeling & Analysis of Interconnects, 12 Applying Test & Measurement Methodology

Description: The IEEE 802.3ck Task Force is developing physical layer (PHY) specifications for operating speeds of 100 Gb/s, 200 Gb/s and 400 Gb/s based on 100 Gb/s signaling per electrical lane. Developing test and validation processes and philosophies often incur questions which may not be immediately evident on reading the specification; the paper is to assist with that understanding.

Thursday, January 30th | 3:45 pm

Panel – PCIe 32G & 64G: System Design & Test Challenges

Click here to view Presentation.

Presenters: Steve Krooswyk, Rita Horner, Ying Li, Dan Froelich, Pegah Alavi, Patrick Casher, David Bouse, Rick Eads, Tim Wig

Room: Ballroom F

Track Name: 07 Optimizing High-Speed Serial Design

Description: As PCI Express 5.0 system development commences, 64G-PAM4 has been announced to follow in 2 years. Join our panel to discuss the challenges in PCIe 5.0\6.0 system designs and validation.

Thursday, January 30th | 4:15 pm

Panel – How To Become An Industry Influencer

Presenters: Istvan Novak, Antonio Ciccomancini-Scogna

Room: Chiphead Theater

Track Name: Chiphead Theater Discussion

Resources

Papers

Current Distribution, Resistance, and Inductance in Power Connectors – DesignCon 2020 Best Paper Award

Finding Reflective Insertion Loss Noise and Reflectionless Insertion Loss

Presentations

Current Distribution, Resistance, and Inductance in Power Connectors – DesignCon 2020 Best Paper Award

Finding Reflective Insertion Loss Noise and Reflectionless Insertion Loss

Panel – PCIe 32G & 64G: System Design & Test Challenges

Demonstration Videos

70 GHz High-Performance Test Solutions

Direct Connect™ to the Silicon Package

112 Gbps PAM4 Front-Panel to Mid-Board – Samtec Flyover®

A Cable Backplane Solution for 112 Gbps PAM4 Architecture

Scott McMorrow: Optimizing 112 Gbps PAM4 Interconnect Design Leveraging ANSYS® HFSS™