Popular topics at SC23 included Exascale and quantum computing, AI and machine learning, and cybersecurity, among others. CXL is one of those hot topics.

Largely used by designers of data center servers, supercomputers, and enterprise computing systems for applications like AI and machine learning, CXL enables cache coherency between CPUs and external devices.

CXL 3.0 leverages PCIe® 6.0 electrical and physical layers at 64 GT/s. It also improves latency in memory and storage use cases.

Matt Burns, Director of Technical Marketing at Samtec, gives an overview of a live product demonstration of a CXL 3.0 AI chassis with excellent performance, operating at 64 GT/s.

Working with our friends at Alphawave Semi, we see a prototypical PCIe 6.0 AI hardware design. This includes a motherboard combined with add-in cards with top card connectivity.

An Alphawave PipeCORE and PiCORE generate CXL 3.0 traffic, running at PCIe 6.0, 64 GT/s PAM4 data rate.

The signals travel through a Samtec BE70A, Bulls Eye® high-performance test point system, through low-loss coax, to Samtec 1.85 mm precision RF connectors located on add-in-card number one.

The signal then travels through the card, through a Samtec HSEC6-DV micro edge card connector, to a rigid backplane. It then travels through 14” (35.6 cm) of backplane PCB, to another HSEC6-DV edge card connector, then to add-in card number two, and back to the Alphawave PipeCORE and PiCORE for analysis.

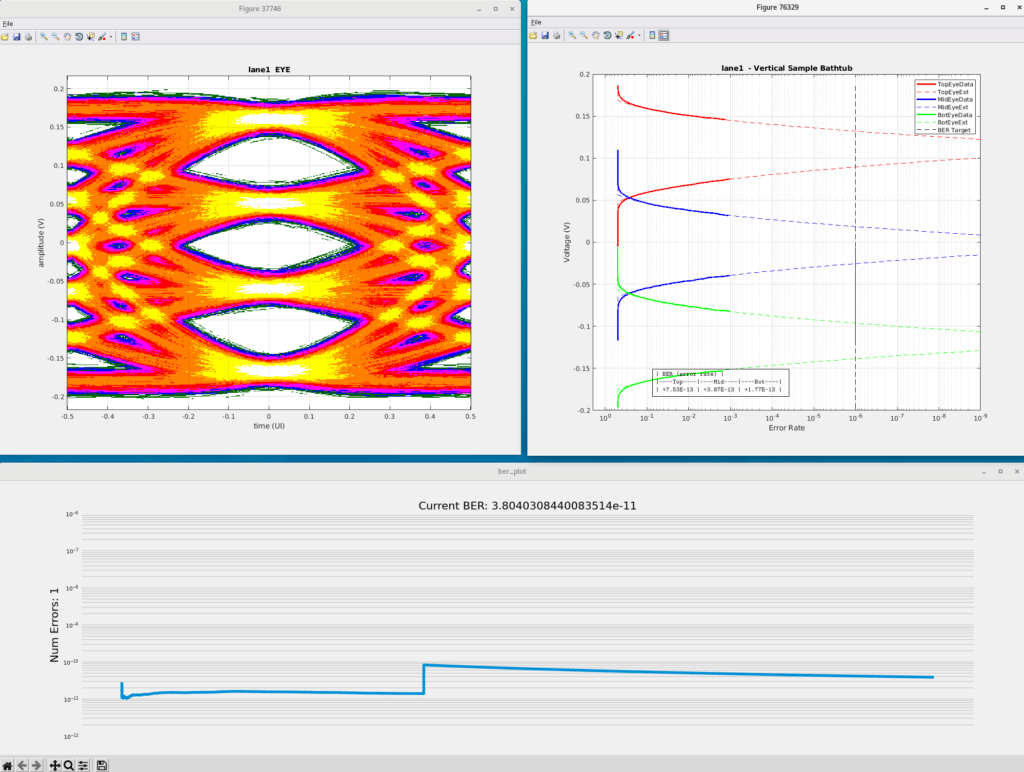

The performance is excellent: the BER is e-11, very clean eye diagrams, and very clean bathtub curves

This demonstration shows that Samtec high-speed interconnect systems can effectively operate in 64 GT/s platforms, including PCI Express 6.0 AI, ML, and HPC applications.

If you have any questions about this demo, please contact us at [email protected].

If this blog interested you, you might also be interested in these:

Leave a Reply