Transceivers. SerDes. XCVRs. Tx/Rx. Yada, Yada, Yada. FPGA designers want more of them. FPGA designers want them to be faster.

Thankfully, the leading FPGA suppliers are answering the call. The Samtec blog features many solutions from Xilinx, but what about Intel? What options are they promoting?

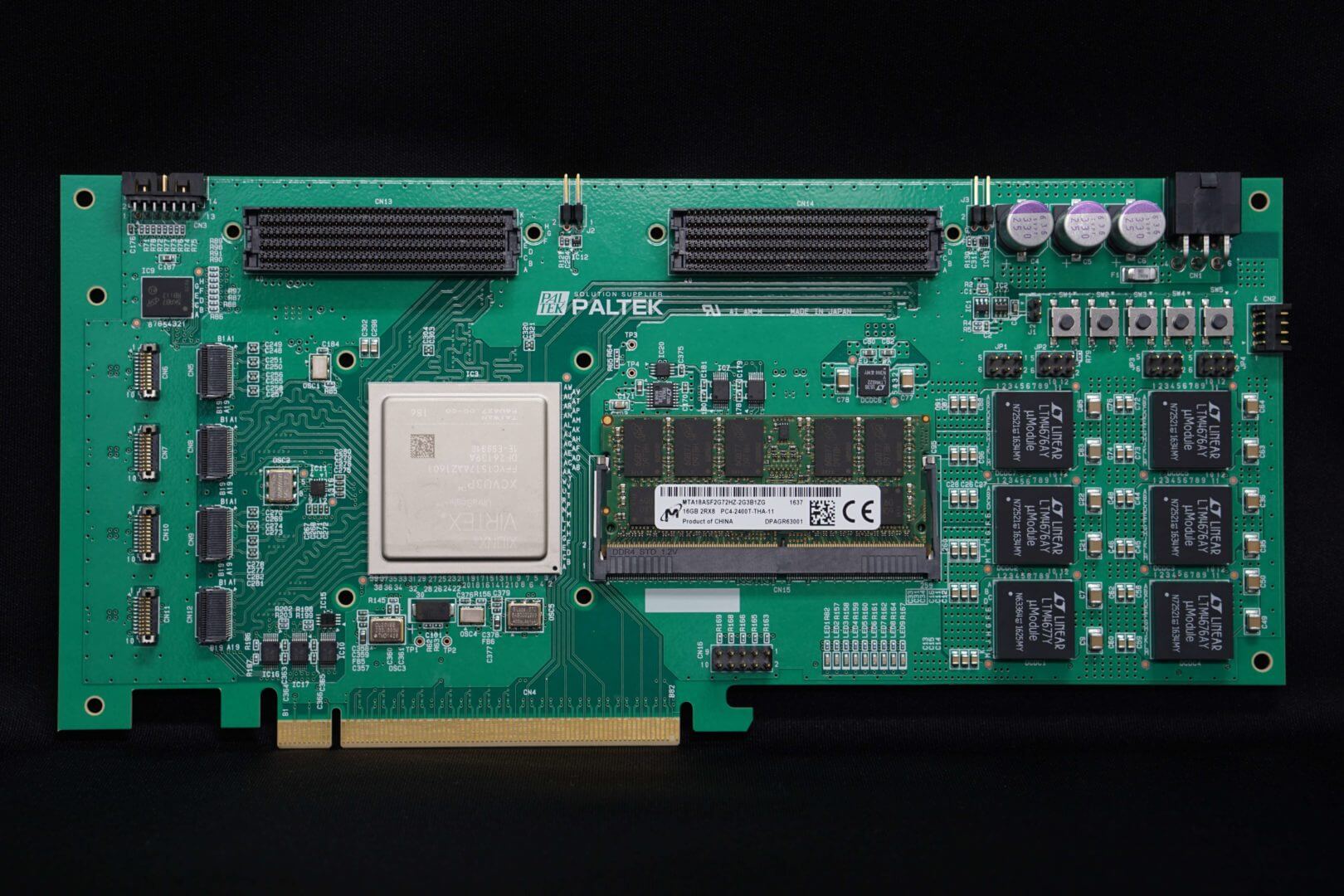

Intel® Agilex™ FPGA and SoCs

Intel recently released their latest FPGA/SoC platform called Intel® Agilex™. This family leverages Intel’s 10nm process technology and advanced architectures. Typically, this approach increases performance and lowers power across next-gen data center applications.

For transceivers, the Intel® Agilex™ F-Series FPGAs and SoC FPGAs are optimized for high-performance in a variety of applications. They also support data rates up to 58 Gbps. They feature up to 112 transceivers across the family.

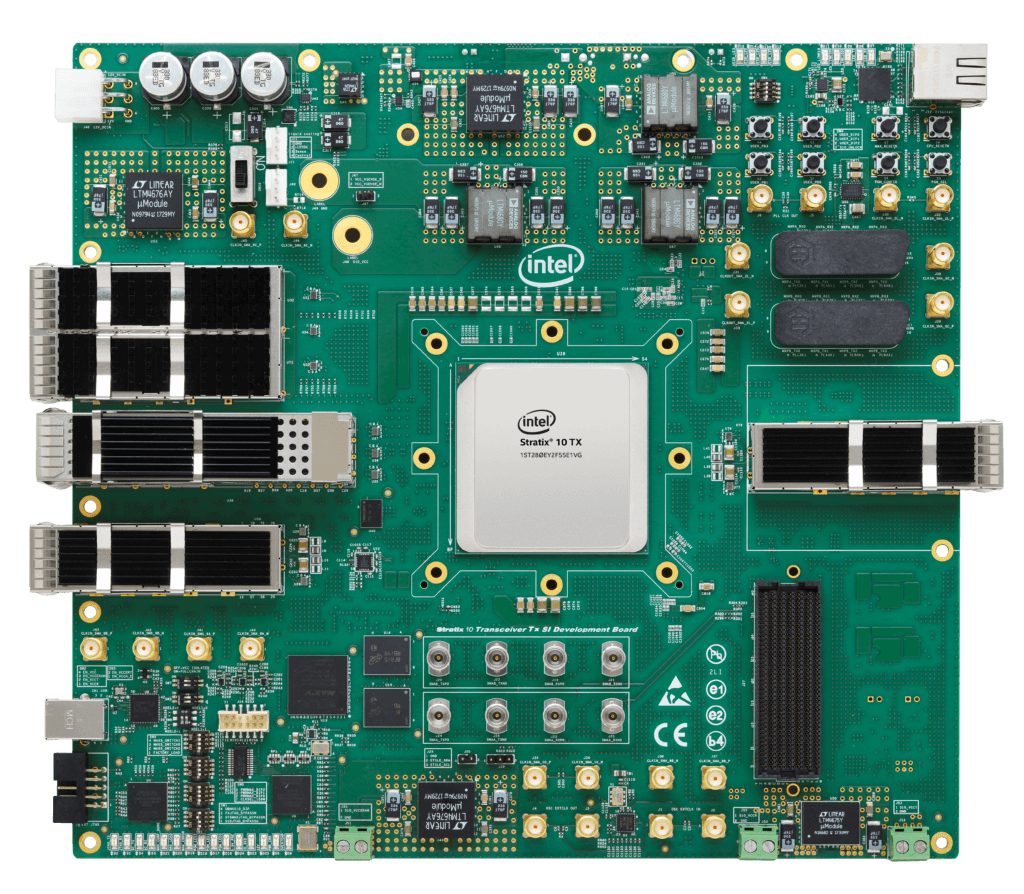

Intel® Stratix® 10 TX Signal Integrity Development Kit

Intel® Stratix® 10 TX FPGAs are the workhorse solution for current designs that require high-speed transceivers. Stratix® 10 TX FPGA transceivers are very flexible. They offer dual-mode capabilities, enabling 56 Gbps PAM4 or 30 Gbps NRZ data rates.

One key development board for Stratix® 10 FPGAs is the Intel® Stratix® 10 TX Signal Integrity (SI) Development Kit. It provides a complete design environment for evaluation of the latest FPGA transceivers.

This kit also features a VITA 57.4 HSPC FMC+ connector for I/O expansion.

What is VITA 57.4 FMC+

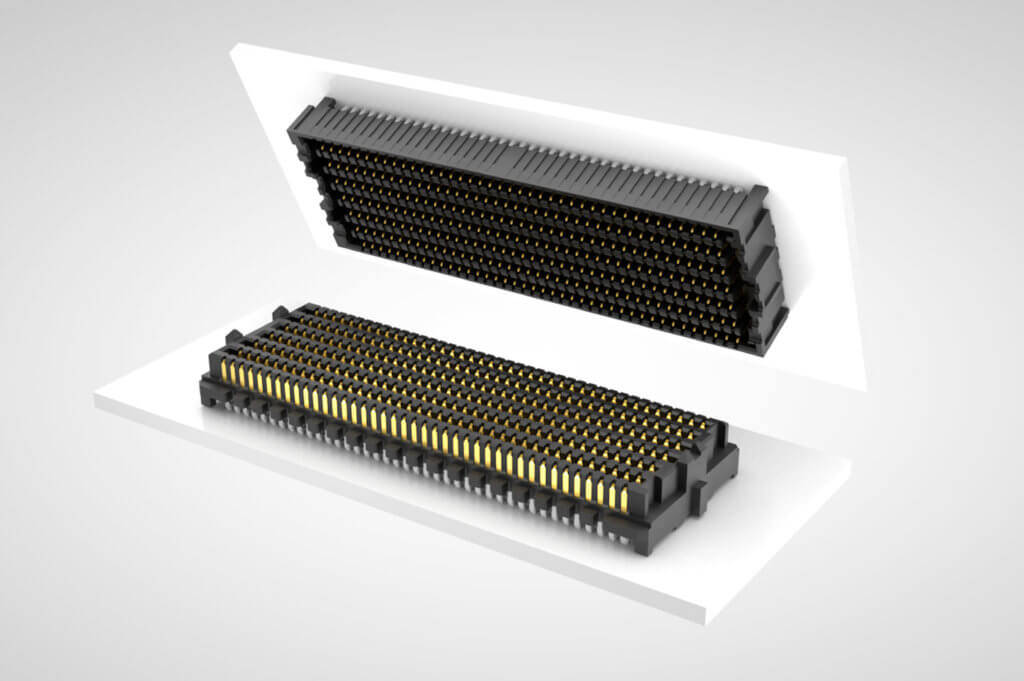

VITA 57.4 FMC+ is the latest standard in the popular VITA FMC family. This specification increases total number of MGTs to 32 and increases the maximum data rate to 28 Gbps.

FMC+ employs a larger connector from the SEARAY™ family of high-speed, high-density arrays. This High Serial Pin Connector (HSPC) has 560 pins arranged in a 14 x 40 array. The HSPC connector supports 24 MGTs.

New FMC+ cards can only plug into new FMC+ carriers due to their larger connectors. Thankfully, original FMC cards will also fit into FMC+ carriers. A customized polarization system provides true backward compatibility.

Additionally, there is an optional extension connector (HSPCe) to boost pin-count by 80 positions, arranged in a 4 x 20 array. HSPCe supports another 8 MGTs for a total of 32 MGTs in the new interface.

For more information, please visit the FMC and FMC+ standards pages.

[…] Source: https://allaboutfpga.com/fpga-architecture/ Source: https://blog.samtec.com/post/new-intel-fpga-platform-features-samtec-interconnect/ […]