Our friends at EDN recently published Solving Signal Integrity Problems At Very High Data Rates. The article – written by Lee Ritchey and Kella Knack from Speeding Edge and Teraspeed’s own Scott McMorrow – discusses the challenges of achieving high data rates given parasitics in PCBs. It presents a novel, alternative design approach to the problem.

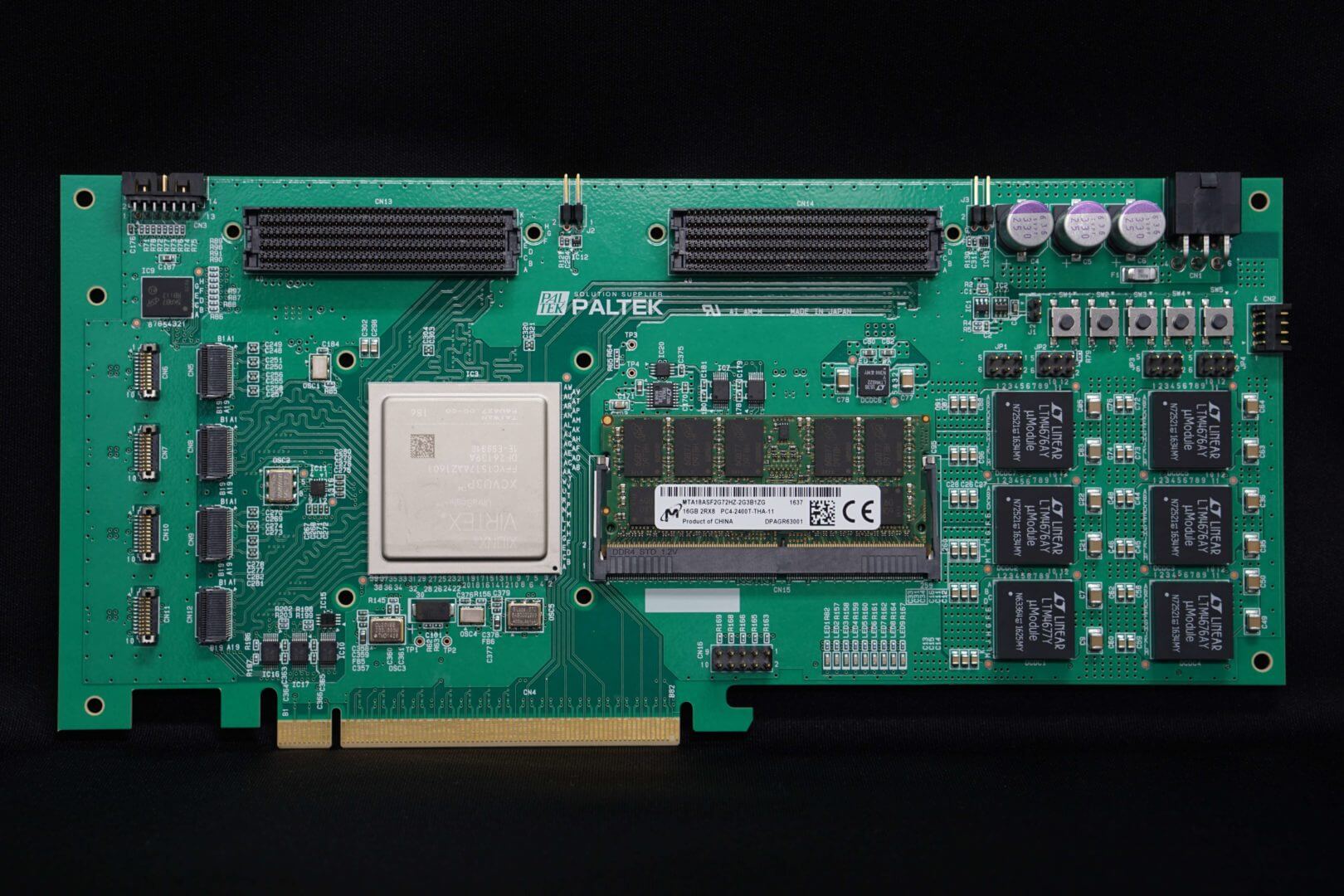

To elaborate a bit … Advances in semiconductor technology are making it possible to connect components in products such as switches and routers at data rates up to 56 Gbps. As these higher speeds are achieved, micro-scale variations in the materials used to fabricate PCBs and backplanes can significantly degrade signals.

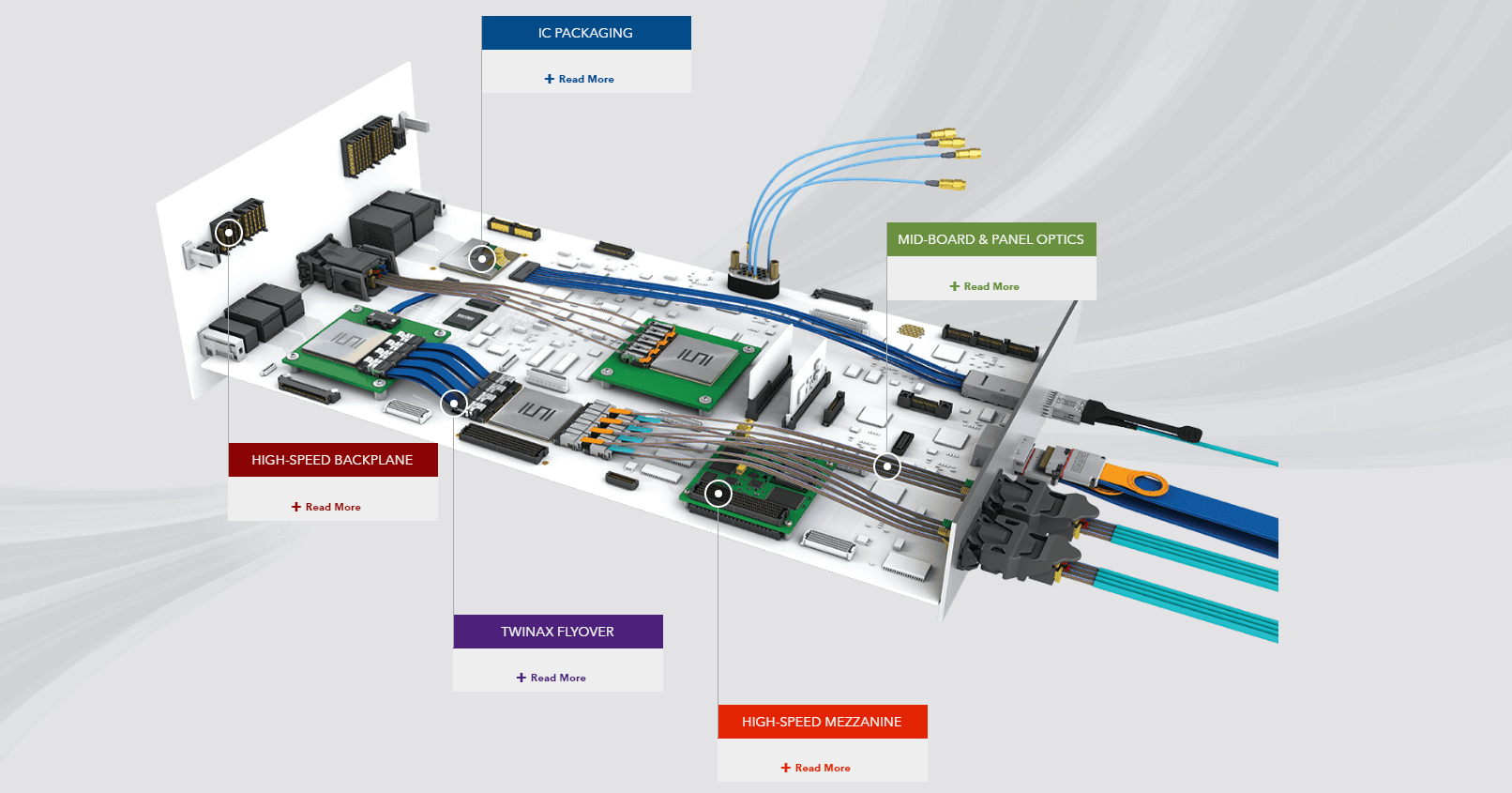

Among the problems encountered are loss, skew, cross talk and degradation due to the parasitic capacitance of the plated through holes required to mount the connectors to the backplanes and daughter cards.

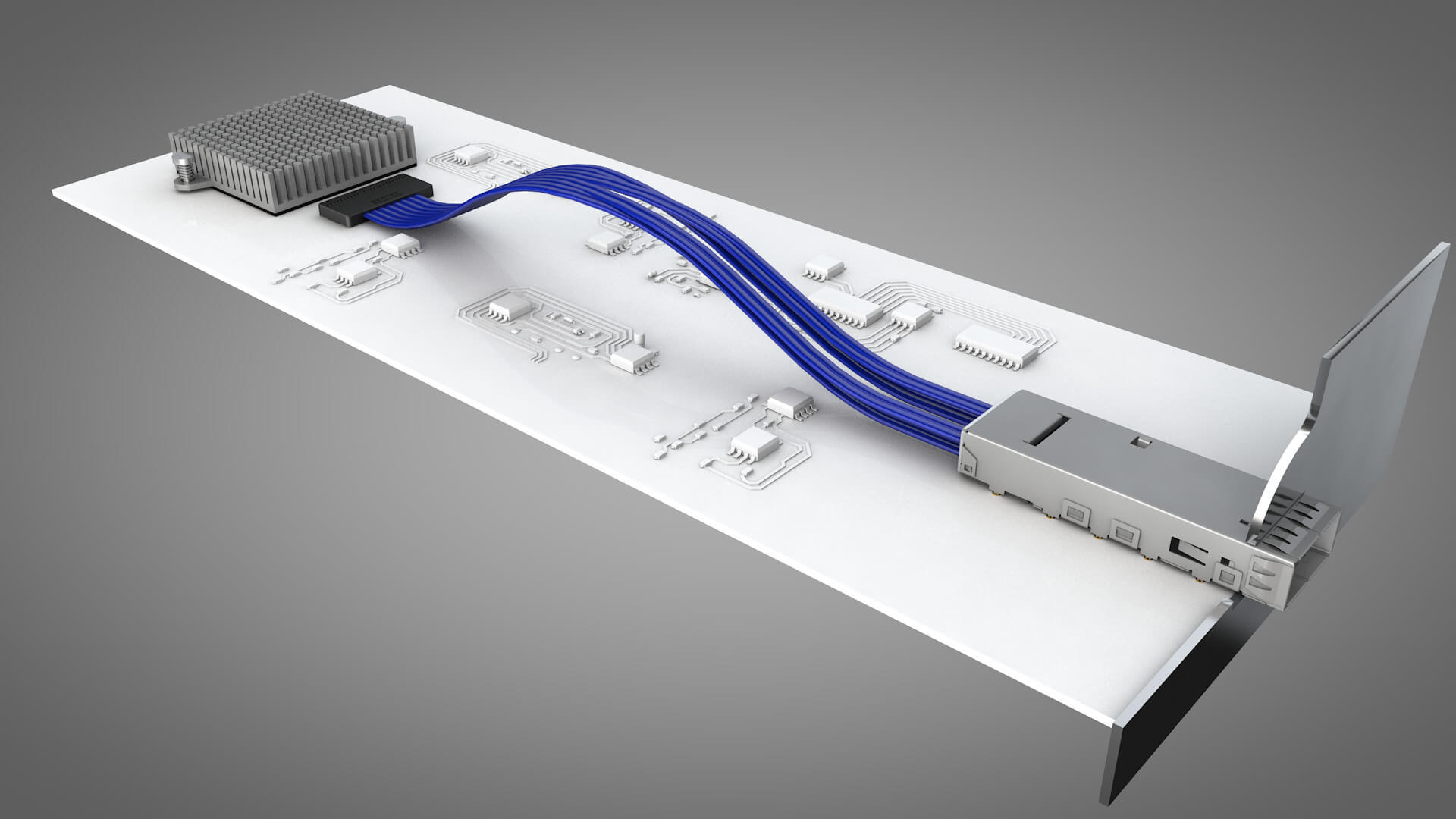

Removing these signals from those PCBs and backplanes can solve the problem. Using Twinax cables to make these connections instead of implementing them in the PCBs and backplanes with traditional traces minimizes these effects.

Skew, cross talk and degradation from the plated through holes can be virtually eliminated. Due to the ultra-low loss of the Twinax cables, the lengths of paths can be made longer or the frequency of operation can be extended much higher than is possible with the laminate systems currently available.

Other links that may be of interest: