“Artificial Intelligence” and “AI” are all the rage. From high frequency trading on Wall Street to improved drug development, AI affects more aspects of human lives daily.

Many AI solutions harness the computing power of cloud connectivity, edge computing, data centers and HPC. There are any number of resources that discuss the best frameworks and learning algorithms. But what about the hardware?

That is the goal of the AI Hardware Summit, being held September 17-18, 2019 at the Computer History Museum in Mountain View, CA. The event will raise awareness of next-gen silicon & systems used in processing deep learning, neural networks & computer vision.

Samtec will be demonstrating several next-gen interconnect architectures related to AI-focused silicon and systems.

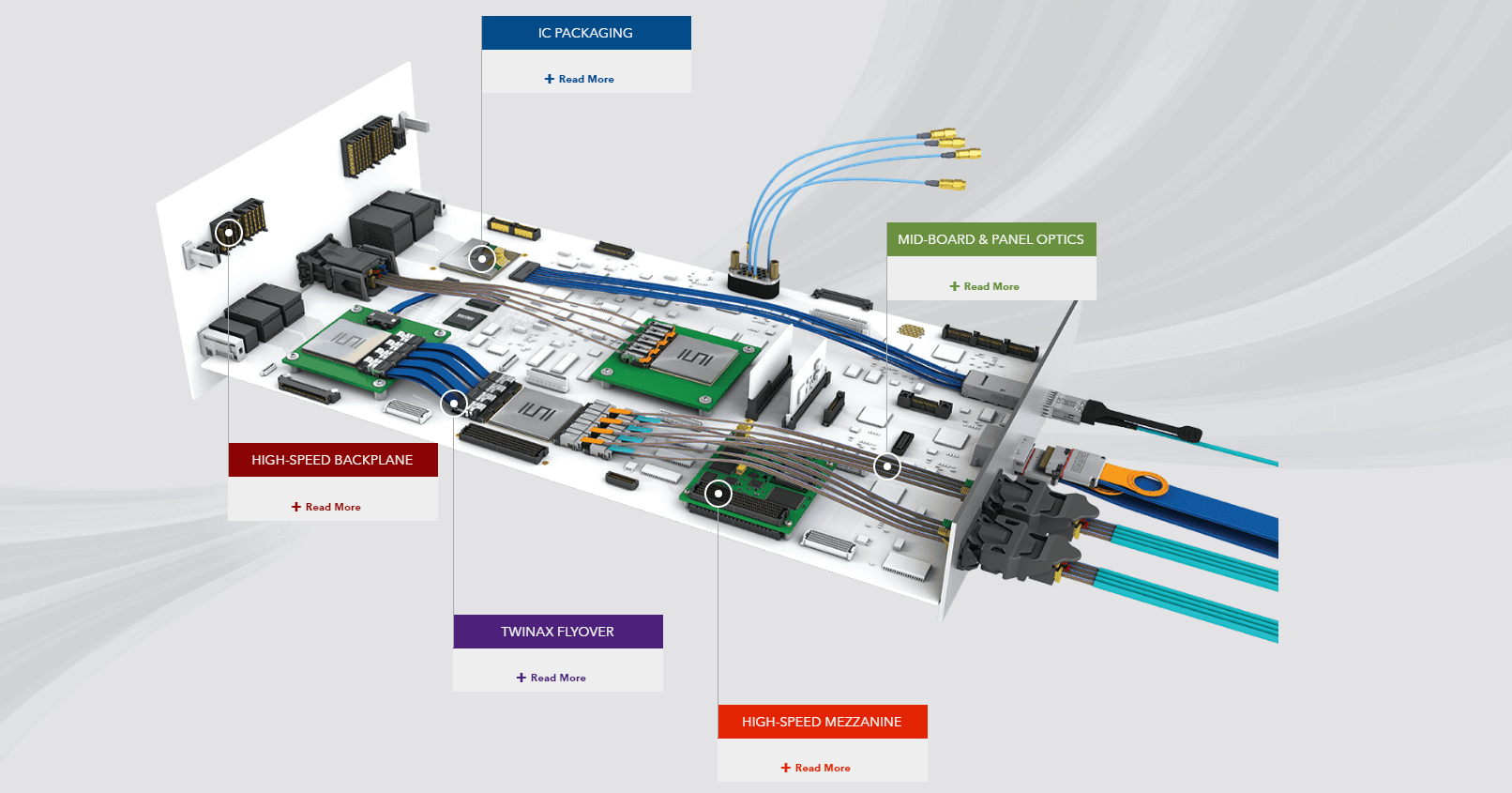

Scalable 32 GT/s Silicon Test Platform for AI

AI hardware systems are highly-complex. Samtec and its partners have developed a configurable, next-generation GPU-based system combining a cable mesh backplane (AcceleRate® Slim Body Cable Assemblies) and next-generation High-Speed Edge Card Connector topologies.

This is a demonstration of configurable, next-generation GPU-based system combining a cable mesh backplane (AcceleRate® Slim Body Cable Assemblies) and next-generation High-Speed Edge Card Connector topologies.

The demonstration incorporates an Artificial Intelligence, Machine Learning style interconnect based on the Gen-Z PECFF form factor. The topology incorporates up to eight risers that include PCIe Gen5 AI usage models, and the Samtec Flyover® concept.

The system provides scalability of the PCB and cable interconnect via moving add-in cards and swapping cables, all operating within PCIe Gen 3, Gen 4, and Gen 5 performance requirements.

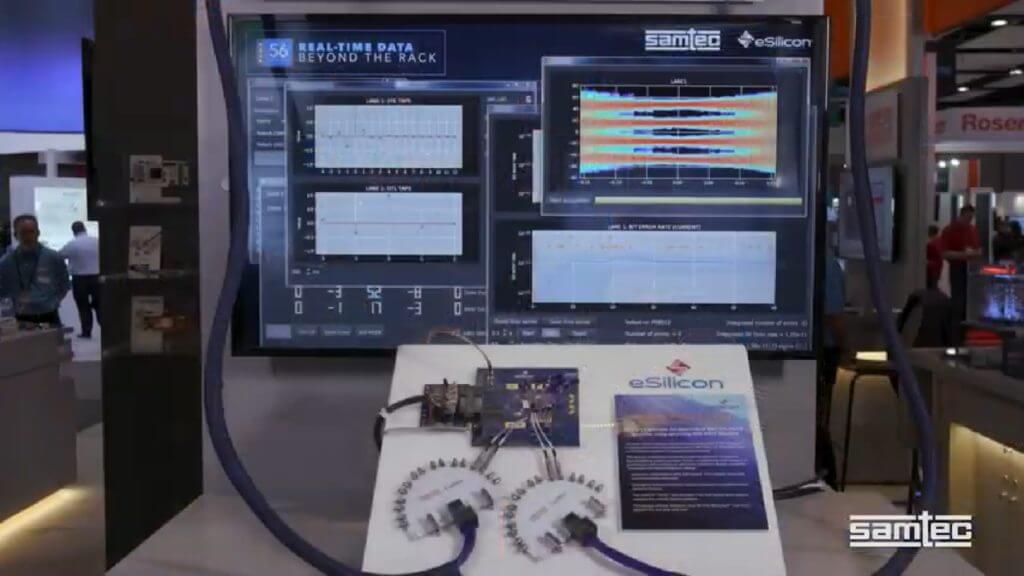

56 Gbps PAM4 Active Product Demonstrator

The 56 Gbps PAM4 Active Product Demonstrator showcases Samtec’s comprehensive portfolio of high-performance interconnects in a typical data center chassis application.

It offers a complete system design based on Credo Semiconductor SERDES ICs that measure and display 56 Gbps PAM4 performance over 88 lanes. Key features of the demo include:

- PRBS-31 generated 56 Gbps PAM4 Data Rate

- Analyzes performance across all channels

- Bit Error

- Eye Height

- Eye Pattern

- Key products included

Booth-to-Booth – 58G DSP-Based SerDes over 5m Copper Cable

Booth-to-booth over 5m of copper cable? How? At 56G PAM4 data rates? That can’t be right, is it? For that to take place, a good SerDes would be the first step.

Fortunately, eSilicon has the perfect solution. eSilicon makes tuning 58G SerDes easier by using novel DSP-based architecture. This approach to SerDes design offers performance, versatility, improved power efficiency and long-reach support on next-gen 7nm FinFET technology.

Additionally, the 58G DSP-Based SerDes support industry protocols common in the data center. These include a wide variety of IEEE and OIF-standardized protocols including Ethernet and Fibre Channel.

Samtec’s Twinax Flyover® technology enables data to reach beyond the rack. In order to accomplish this, Samtec’s ultra-low skew twinax cable must extend signal reach and density at 56G PAM4 when compared to noisy and lossy PCBs.

Samtec Flyover® Technology is typically used front-panel to mid-board, or mid-board to backplane. However, Samtec’s crack squad of high-speed cable design engineers have developed a prototype 5m EBCM series ExaMAX® Backplane Cable Assembly.

Reaching beyond the rack has been brought to the AI industry by Samtec and eSilicon. Stop by the Samtec booth #22 and the eSilicon booth #21 at the AI Hardware Summit for more details.

Leave a Reply