The full PCIe® 6.0 specification in nearing completion. The latest 0.9 version provides details on increased system data rate to 64 GT/s, doubling the throughput from PCIe 5.0. Additionally, the latest version further explains PAM4 encoding, FLIT-based encoding, and low-latency FEC to improve bandwidth efficiency.

In this video, Ralph Page, System Architect at Samtec, walks us through a demonstration of a prototypical PCIe 6.0 AI hardware design based on the GenZ-PECFF form factor. Working with our friends at Synopsys, we see a GENZ motherboard combined with GENZ Add-In-Cards with top card connectivity. It emulates industry standard AI Acceleration hardware platforms.

The Synopsys PCIe 6.0 PHY generates up to four 64 GT/s PAM4 differential signals.

The differential pairs route through an Isola Tachyon 100 G test board, to a Samtec 70 GHz Bulls Eye® High-Performance Test System (the BE70A Series), through 20” (51 cm) of low-loss coax cable, to Samtec 2.40 mm precision RF connectors on the first add-in card.

A Tale Of Two Signal Paths

From this point, we’re going to look at two different signal paths. Very simply put, the first signal travels through the backplane, and the second travels through high-speed cable assemblies.

More specifically, the first path travels from the add-in card, through a Samtec HSEC6-DV micro edge card connector, to a rigid motherboard that’s populated with eight HSEC6-DV connectors.

The signal then travels through a little over 5″ (13 cm) of backplane, to another HSEC6-DV micro edge card connector, to a second riser card, then back to the Synopsys device for analysis.

The second signal path also begins at the first add-in card, but this one instead routes to a Samtec Flyover® cable system on the top side of the card. The AcceleRate® cable system consists of an ARF6 right-angle PCB connector, and an ARC6 cable assembly with 18″ (46 cm) of Eye Speed® ultra-low skew twinax cable.

These signals travel from the cable assembly, to another AcceleRate connector system on the second add-in card, through 2.40 mm precision RF connectors, and back to the Synopsys PHY.

Looking Good …

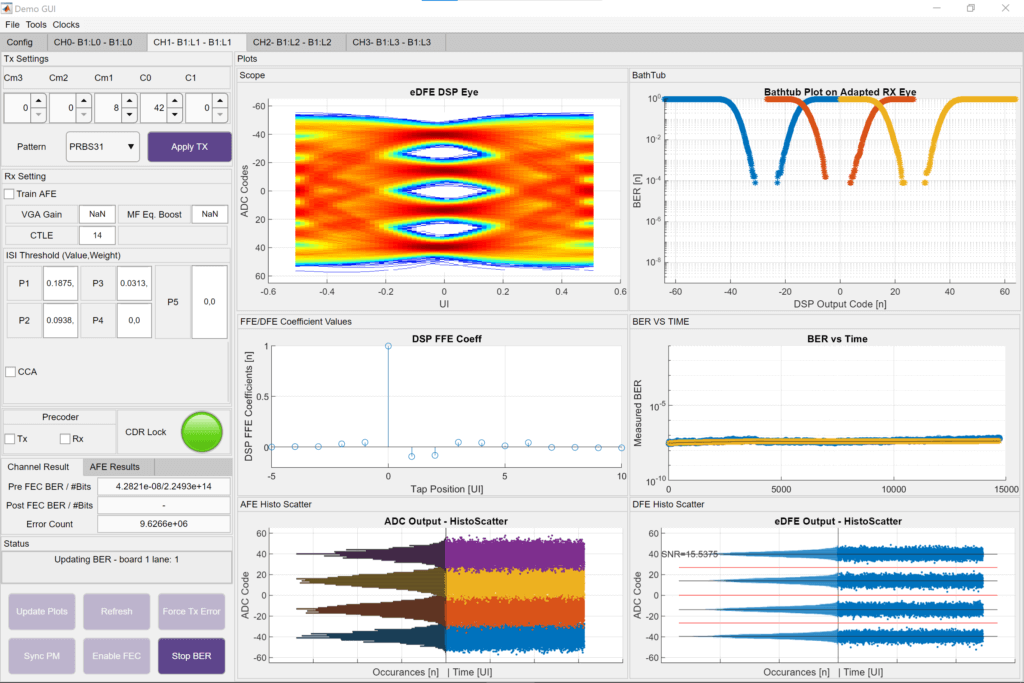

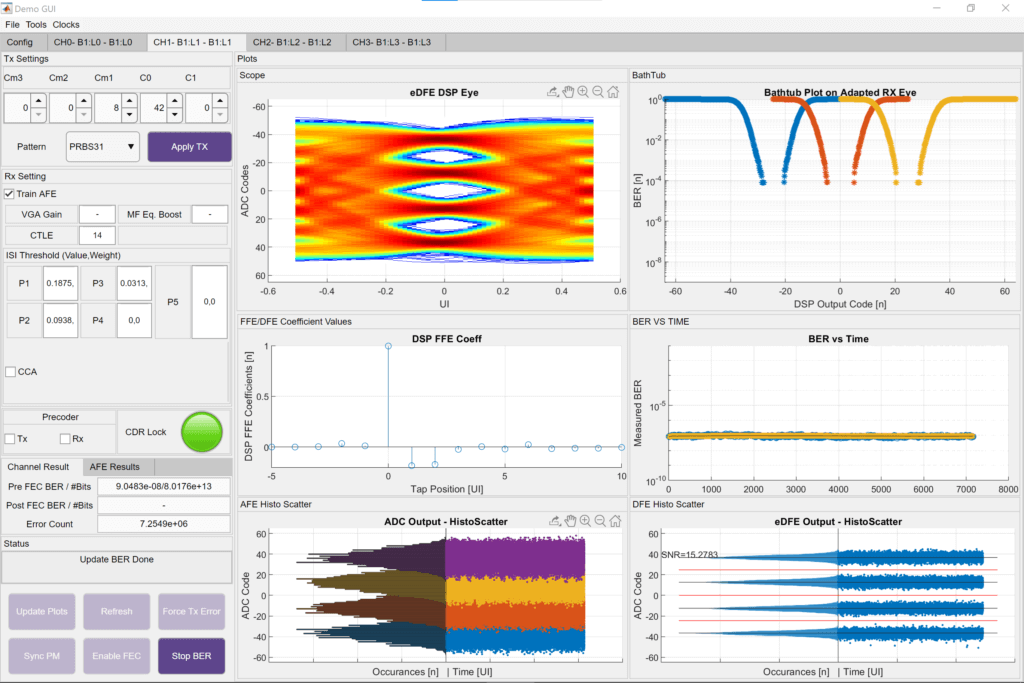

In Ralph’s own words, the results are excellent. Again, the demo has two signal paths — one through the rigid backplane, and one through the AcceleRate cable system.

Looking at the rigid backplane, we see the eyes are wide open, and we see an incredible bit error rate of e-8 at 64 GT/s.

Looking at the results of the AcceleRate cable system with 18″ of flexible Eye Speed twinax cable, the bit error rate is even better, and the eyes are wide open.

This demonstration shows that Samtec Flyover technology and high-speed interconnect systems can effectively operate in 64 GT/s platforms that incorporate multiple riser cards that include PCI Express 6.0 AI, ML usage models.

More Info About Samtec and PCIe 6.0

If you have any questions about this demo, please contact us at [email protected]

Here’s a similar PCIe 6.0 blog/demo that may also be of interest.

Leave a Reply