Summer is here. The kids are out of school. Families are taking well-deserved holidays and vacations or even enjoying local staycations.

Even though it’s summer, design engineers still need to move their new projects along. Additionally, designers need to keep their skills sharp and learn about the latest tools. Some upcoming webinars will no doubt help the engineering community stay updated on FPGA SoMs, expansion buses and associated interconnects, and the latest on PCI Express® specifications.

Keep reading for more details!

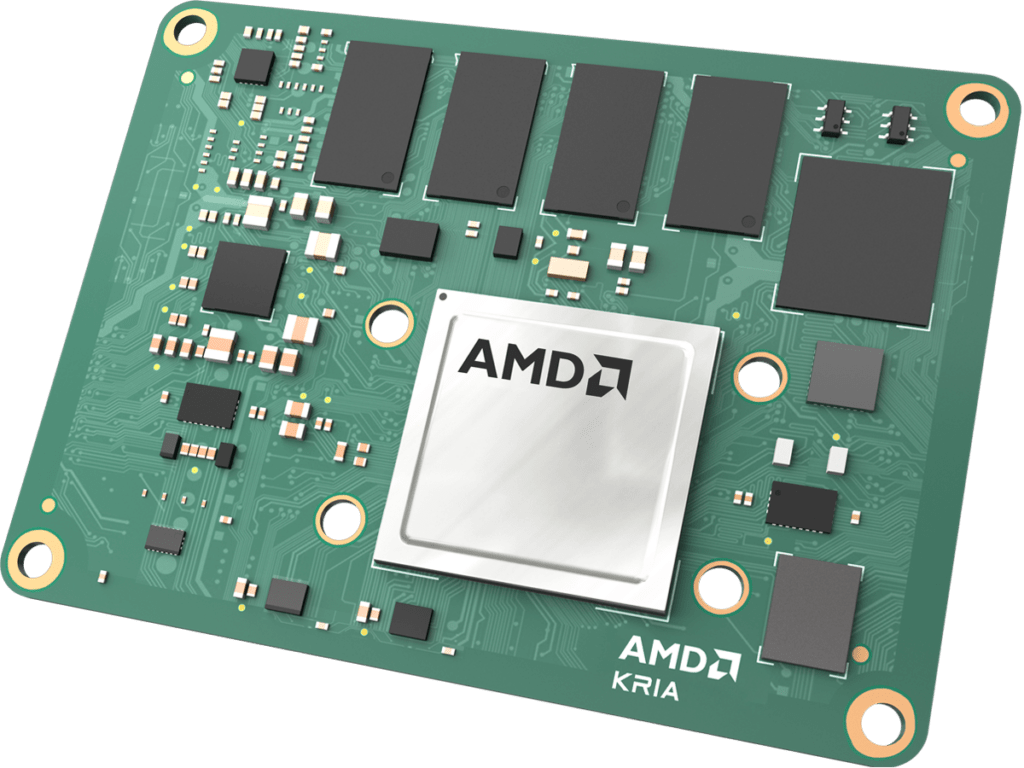

AMD KriaTM SOM – Tuesday, July 25, 2023

FPGA SoMs shorten design cycles and provide the simplest path from prototype-to-production. AMD Kria SOM solutions offer small form factor card is ideal for production deployment in Smart Camera, Embedded Vision, Retail Analytics, Smart City, and Machine Vision application.

The new Kria K26 SOM has been ruggedized for industrial life cycles. A Kria K26 SOM can also become the adaptive compute solution for intelligent factory assets and provides a simple path from concept to production through future hardware design revisions.

In an upcoming webinar entitled “Kria App Series: Roadmap For Your Hardware Design“, technical experts from AMD and Samtec will focus on the advantages of designing new hardware with the Kria K26 SOM Find out about available resources to start your own custom carrier design for your end application. Also, discover what solutions are provided to help accelerate your own product development work.

Learn about resources available for the Kria starter kits on the market today and how to fully leverage them for hardware differentiation and shortening the runway to volume deployment of your own unique solution using the K26 SOM.

Register here for the free, one-hour webinar.

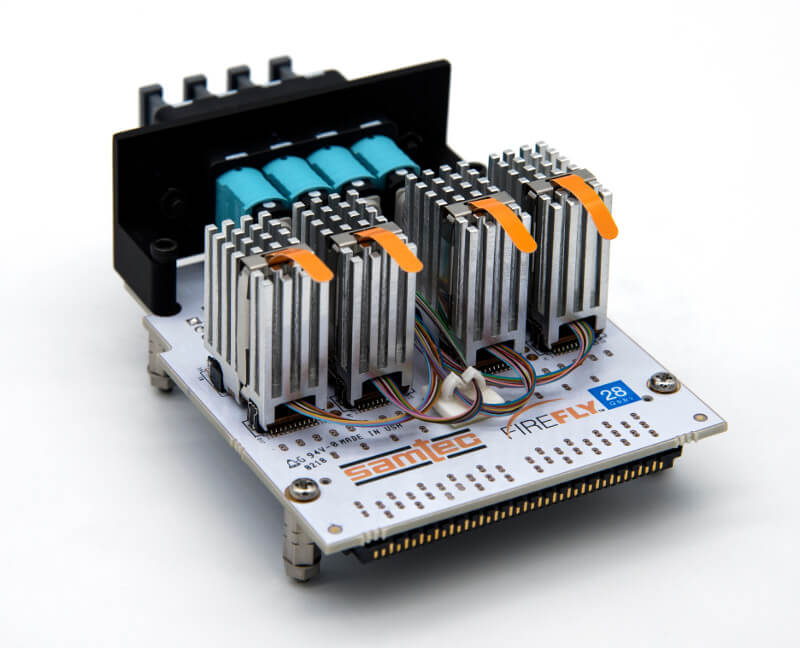

Mouser – Wednesday, July 26, 2023

The ecosystem of FPGA/SoC Development Kits and Daughter Boards continue to expand. What was once a two-vendor market has morphed into multiple FPGA/SoC solutions targeting applications from basic embedded devices to the intelligent edge. Electrical engineers and system architects need easy-to-use Development Kits and Daughter Boards for rapid system prototyping.

However, what expansion standards are available? What expansion standard makes sense for a specific application? In an upcoming webinar entitled “Understanding FPGA/SoC Expansion Options for Rapid Prototyping“, technical experts from Samtec will compare and contrast FPGA/SoC expansion standards including PMoD, CRUVI, SYZYGY®, VITA 57.1 and VITA 57.4.

In additional, technical details on appropriate FPGA/SoC expansion buses development tools and interconnect will be presented. This webinar takes a look at:

- What expansion standards are available

- What expansion standard makes sense for a specific application

- What is the performance of different expansion options

- How these options improve FPGA development

Register here for the free, one-hour webinar.

PCI-SIG®- Thursday, July 27, 2023

For more than two decades, PCI-SIG® has delivered industry-leading PCI Express® (PCIe®) specifications, remaining ahead of the demand for a high-bandwidth, low-latency interconnect for compute-intensive systems. Starting with the PCIe 1.0 specification in 2002, PCI-SIG has doubled the I/O bandwidth with each subsequent generation. Considering the entire catalogue of PCIe specifications, there are many different factors to consider when choosing the right PCIe generation for an application. Factors might include power, bandwidth, signal integrity, reach and data transfer rates.

In this an upcoming webinar entitled “Exploring the Technical Differences Between the PCI Express Specifications”, panelists from Astera Labs, Microchip, Samtec and Synopsys will discuss the technical differences between the PCIe specifications. The PCIe 4.0 and PCIe 5.0 specifications (16 GT/s and 32 GT/s) are the current industry standards. PCIe 6.0 (64 GT/s) technology market adoption is now underway. The PCIe 7.0 specification is under development and on track for release in 2025. The new standard will target 800 GbE, AI/ML, Cloud and Quantum Computing and Hyperscale Data Centers applications.

Participants will learn the technical considerations of PCIe technology, including:

- Differences in electrical signal reach between the PCIe specifications

- Maximum latency for each PCIe technology generation

- Challenges of PCIe 5.0 specification adoption and the jump to PCIe 6.0 technology

- Shift from NRZ to PAM4 signaling

- The diverse applications of PCIe technology and implementation approaches

Register here for the free, one-hour webinar.

Leave a Reply