Samtec will be supporting a variety of experiences for attendees at DesignCon 2023. Read on to find out what to expect from Samtec!

For help with DesignCon 2023 registration, head to our show page here to receive a free Expo Pass and 20% discount for conference passes.

Blast Off at Tuesday’s Welcome Reception!

Be our guest at the 2023 Welcome Reception, Tuesday 31 January from 6-8 PM in the Hyatt’s Santa Clara Ballroom with a tribute to engineers’ contributions to space exploration. Check out the lunar camera demo, learn about the equipment, and take a selfie with the technology used to transmit pictures from the moon!

Author Meet & Greet on Wednesday 2:30PM

Istvan Novak has worked with IEC to create a new edition of Power Distribution Network Design Methodologies, which includes selected DesignCon papers from the past. Stop by the Samtec booth (#939) February 1 from 2:30-3:00 to meet Istvan and see his book. He will be joined by Eric Bogatin, Steve Sandler, and Peter Pupalaikis, who will be there to talk about their latest books as well. If you have one of their books, bring it along to have it signed! You can also enter to win a signed copy.

Product Showcase on Wednesday 3:00PM

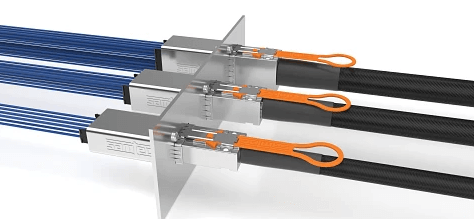

Come see Samtec technologists showcase high-speed interconnects staged for 224 Gbps signaling, and stay to learn about the power connectors and considerations required for these high speeds. Signal integrity is greatly influenced by power integrity, and designing next-generation high-speed interconnects requires careful consideration of both.

Booth Demonstrations Wednesday and Thursday

Samtec will be presenting multiple demonstrations and products that will help you design systems at 112 Gbps, as well as set you up for 224 Gbps. Stop by and learn more about Samtec’s silicon-to-silicon solutions, including Accelerate®, mPOWER®, Si-Fly™, and NovaRay®products. By combining our expertise in signal integrity, advanced products, flexible designs, and Sudden Service, we are prepared to help you solve all of your interconnect needs. Join us at DesignCon23 to meet our team and talk about your design needs!

Around the Show Floor

Samtec products will be featured in demos throughout the show floor. As you make your way around the expo, be sure to stop by and see the technologies on display at Rohde & Schwarz (Booth #1049) and Keysight (Booth #1039).

Check out the podcast below for a quick preview of Samtec’s offering at DesignCon 2023.

Technical Sessions Tuesday-Thursday

Samtec’s signal integrity and power integrity experts will be presenting the following Panels and Papers:

Panel – PCIe 6.0: Challenges of Achieving 64GT/s with PAM4 in Lossy, HVM Channels

January 31 (Tuesday), 4:45 – 6:00 PM, Ballroom F

Panelist: Steve Krooswyk, Senior Signal Integrity Design Engineer at Samtec

This panel will focus on the latest evolution of PCI Express Technology, revision 6.0 of the PCIe spec, which uses PAM4 rather than NRZ signaling of previous PCIe revisions. PCI Express technology’s advances to 64GT/s has enabled system designers to achieve much needed and desired improvements in data throughput aiding advances in the deployment of artificial intelligence inference engines and co-processors in the data center. PCIe 6.0 technology doubles the throughput of PCIe 5.0 devices and ushers in a new, demanding set of chip and system design challenges that IC designers and engineers will have to tackle. To maintain alignment with the tradition of this panel, the panelist will discuss the latest in test and measurement techniques and specs associated with PAM4 signaling. We will also discuss real design and simulation challenges as well as discussions around cables, connectors, and signal integrity issues that designers might face.

Successful PCIe Interconnect Guidelines for 8, 16, and 32 GT/s

February 1 (Wednesday) 9:00 – 9:40 AM, R&S Workshop, Room TBD

Speaker: Steve Krooswyk, Senior Signal Integrity Design Engineer at Samtec

System developers utilizing PCI Express are experiencing increasing pressure to improve interconnect with each data rate increase. To help achieve the maximum routing lengths optimizations for loss, reflection, and crosstalk are all under the microscope. Questions begin to surface – how much optimization is really necessary, or when should I run channel simulation? In this talk we review the ingredients for a successful interconnect and how they change at each speed bump. Practical topics include guidelines for length and loss, the penalty from trace separation and via stubs, connectors, and cables, and interpretation of channel simulation results.

112 Gbps PAM4 Front Panel Connectivity – Real World Implementation and Correlation

February 1 (Wednesday) 11:10 – 11:50 AM, R&S Workshop, Room TBD

Speakers: Greg Vaught, VNA Product Planning Engineer, Rohde & Schwarz & Matthew Burns, Technical Marketing Manager, Samtec

The road to 112 Gbps PAM4 channels, the basis for 800 Gbps front panel connectivity, is filled with twists, turns, and demanding decisions. Design challenges including breakout regions, PCB stack-up, laminate selection, mechanical concerns, and more are obstacles that must be overcome. Additionally, correlating real-world channels with simulated data offers designers, engineers, and system architects the design assurance of next-gen front panel connectivity solutions. In this webinar, technical experts from Rohde & Schwarz and Samtec will present novel solutions that exceed the demands of next-generation data transmission.

A Novel Approach to 224 Gb/s Reference Receiver Design Using Raised Cosine Response for Noise Mitigation

February 1 (Wednesday) 2:00 – 2:45 PM, Ballroom G

Co-Author: Rich Melitz, Samtec

Since noise is integrated over the entire operating channel bandwidth, its impact must be mitigated by appropriate filtering at the receiver. The 84 GHz cut off frequency of the 4th order Butterworth filter extrapolated from IEEE802.3ck may no longer be sufficient. Discussion within this paper includes aspects of a novel raised cosine (RC) filter, which has a steeper low pass cutoff and can be coordinated with required measurement bandwidth.

Panel – What Users Need from Power Integrity Simulators

February 1 (Wednesday) 4:00 PM – 5:15 PM, Ballroom F

Moderator: Istvan Novak, Samtec

Power distribution keeps getting more and more demanding in a lot of electronic designs and the pre- and post-layout PI simulations are becoming an integral part of the design and validation processes. This panel brings together PI tool users from various OEMs with decades of design experience so that they can summarize and discuss the state of the PI simulation tools the way how they have experienced it and lay out the user needs for additional features and capabilities. A follow-up panel will be devoted to the emerging approaches and solutions offered by CAD companies.

3D Connection Artifacts in PDN Measurements (Best Paper Award Finalist)

February 2 (Thursday) 9:00 AM – 9:45 AM, Ballroom G

Co-Author: Istvan Novak, Samtec

In this paper we will analyze via and trace coupling effects using hybrid and full-wave solvers by deembedding/calibration utilizing multiple test-boards. More sophisticated DUT boards will also be used to look at the parasitic probe-via coupling in two-port shunt-through self and transfer impedance PDN measurements.

Cascaded vs End-to-End Multi-Pin Interconnect Simulation Models (Best Paper Award Finalist)

February 2 (Thursday) 11:15 AM – 12:00 PM, Ballroom H

Speaker: Robert Branson, Samtec

This paper demonstrates the differences between cascaded and end-to-end interconnect models through correlated simulation/measurement models. Field plots are used to show the inaccuracy created by the artificial simulation boundary where the model was cut to perform the cascade. Then we study how to devise mitigation strategies to maintain the decrease to simulation time generated by running cascaded multi-pin connector models while avoiding simulation inaccuracy that is generated through the same process.

Envisioning the Future of Power Integrity through the Eyes of Experience

February 2nd (Thursday) 2:00 PM, Cadence Sponsored Session

Speaker: Istvan Novak, Samtec

This talk outlines Istvan’s personal experience, and then covers why PI is difficult, Golden Triangle, challenges of simulations, measurements, and understanding through case studies, as well as predicting the future.

Panel – Overcoming Career Challenges for Millennials

February 2nd (Thursday) 4:15 PM, Chiphead Theater

Panelist: Robert Branson, Samtec

Moderated by Design News Senior Editor Spencer Chin, the panel will discuss some of the biggest concerns millennials in technology have as they ascend the career ladder.