Samtec high-speed technologies for Silicon-to-Silicon optimization will be on display, including demonstrations of our state-of-the-art 56 Gbps PAM4 Active Product Demonstrator featuring several new products: AcceleRate® mezzanine, ExaMAX® backplane, and Eye Speed®

About Samtec | Featured Products | Featured Events | Presentations | Passes

About Samtec

Samtec, an industry leader in Signal Integrity and micro solutions, offers a broad line of electronic interconnects including Advanced Microelectronics, High-Speed Board-to-Board and Backplane, Samtec Flyover™ and High-Speed Cables, Mid-Board and Panel Optics, Precision and Test RF, Flexible Stacking, and Micro/Rugged components and cables.

This enables us to provide overall “Silicon-to-Silicon” system optimization from the bare die to an interface 100 meters away and all interconnect points in between.

Silicon-to-Silicon System Optimization

As data rate requirements approach and surpass 56 Gbps, developers are challenged with balancing increasing throughput, scalability and density demands with concerns such as power consumption, signal integrity, cost

Featured Products

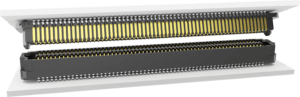

New Samtec Industry-Leading Bandwidth, Density Interconnect System

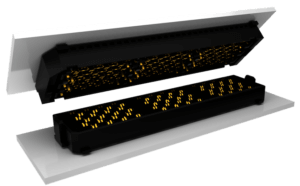

Samtec’s NovaRay™ is an industry-leading high bandwidth, high-density interconnect system.

The innovative pin-to-ground differential pair configuration enables very low crosstalk to 40 GHz+, tight impedance control, and minimal variance in data rate as stack heights increase. The system is 112 Gbps PAM4 capable and is rated up to 56 Gbps NRZ per channel. It boasts an industry-leading aggregate average data rate of 1.33 Tbps per square inch. This extreme performance and density is critical as system sizes decrease while speeds increase.

Two highly reliable points of contact contribute to the 112 Gbps PAM4

The 92 Ω impedance rating addresses both 85 and 100 Ω applications. An improved breakout region has been developed using a new offset signal-to-ground configuration. NovaRay is initially available in a variety of configurations from 8 to 72 pairs, and can easily be expanded to higher pair counts because of its modular design. Board-to-board configurations include 8 pairs / 448 Gbps aggregate, 16 pairs / 896 Gbps aggregate, and 32 pairs / 1.8 Tbps aggregate. Stack heights range from 7 mm to 20 mm. Right-angle and vertical cable options are in development, which will combine NovaRay with Samtec’s industry-leading Eye Speed® twinax cable. Cable and board interconnects are intermateable.

For more information go to samtec.com/novaray.

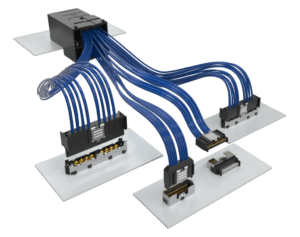

AcceleRate® Cable System Provides Ultra-High Density

Samtec’s AcceleRate® cable assembly is the slimmest in the industry with a 7.6 mm body width ideal for closer proximity to the IC. The high-density 2-row design features 8 and 16 pair configurations on a 0.635 mm pitch for up to 92 pairs per square inch.

Rated to 56 Gbps PAM4, this assembly supports Samtec Flyover™ technology via 34 AWG 100 Ω ultra-low skew

Metal latches on both End 1 and End 2 of the cable connectors are standard, as well as standard and reversed wiring options. The mating PCB level connector is the ARF6 series.

For more information go to samtec.com/accelerate.

Samtec Flyover™ Saves Costs and Improves Performance

As bandwidth requirements rapidly increase, routing signals through lossy PCBs, vias and other components has become one of the most complex challenges designers face. Samtec Flyover™ breaks the constraints of traditional substrate signaling and hardware offerings, resulting in a cost-effective, high-performance answer to the challenges of 28 Gbps bandwidth and beyond. Reducing thermal challenges, eliminating expensive

Samtec’s co-extruded twinax cable technology eliminates the performance limitations and inconsistencies of individually extruded dielectric twinax cabling, leading to improved signal integrity, bandwidth and reach for high-performance system architectures. Samtec’s Ultra-Low Skew Twinax cable is ideal for up to 112 Gbps applications, with tight coupling between signal conductors, improved bandwidth and reach, improved signal integrity and eye pattern opening, and low skew (< 3.5 ps/meter) over extended lengths.

Popular Samtec Flyover cable assembly systems include FireFly™ low profile, high-density systems; FQSFP-DD and FQSFP; slim and high-density AcceleRate®; NovaRay™ extreme speed and extreme density, and ExaMAX® high-speed backplane cable systems (EBCM andEBCF Series).

For more information go to samtec.com/flyover.

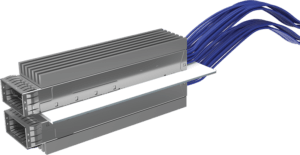

Samtec Expands ExaMAX® High-Speed Backplane Connector System With Backplane Cable Assembly and Direct Mate Orthogonal (DMO) Options

Samtec’s new ExaMAX® Direct Mate Orthogonal (DMO) solutions offer system designers flexibility by removing the midplane, allowing fabric cards and line cards to mate directly. This fast-growing system architecture increases airflow and improves thermal efficiencies throughout the chassis. DMO solutions enhance signal integrity via shorter trace lengths and less connector transitions while streamlining the system BOM and optimizing system cost.

Samtec’s ExaMAX® DMO system consists of the new EBDM-RA series which mates directly with existing EBTF-RA series. They are currently available in 6-pair and 6, 8, 10, and 12 columns. Guide pin and screw mount options are also available.

ExaMAX high-speed backplane cable assemblies, EBCM

A Samtec ExaMAX backplane cable assembly was recently featured in an error-free, 56 Gbps PAM4 demonstration without

The ExaMAX® line of products is optimized for speeds up to 56 Gbps (PAM4 modulation). Return loss compliance is achieved in both 85 Ω and 100 Ω systems due to targeting the 92 Ω specifications and controlling reflections at all geometry transitions within the connector. ExaMAX® also has the industry’s lowest mating force with excellent normal force and meets Telcordia GR-1217 CORE specifications. With two reliable points of contact at all times, even when subjected to angled mating, residual stubs are minimized for improved signal integrity performance. A 2.4 mm contact wipe increases reliability while the hermaphroditic mating interface ensures stub-free mating and reliable alignment.

The backplane system features individual signal wafers with differential pairs in a staggered design and arranged in columns with zero skew. Each wafer includes a one-piece embossed ground structure, which increases isolation to significantly decrease crosstalk.

For more information visit the ExaMAX® High-Speed Backplane Connector System landing page, or download the High-Speed Board-to-Board Application Design Guide. Immediate technical support is available from Samtec’s backplane applications experts at [email protected].

For more information go to samtec.com/examax.

ExaMAX® is a registered trademark of AFCI

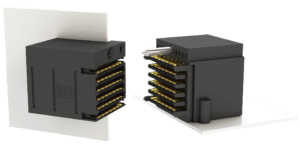

Samtec Introduces New High-Density, High-Speed Micro System

Samtec’s AcceleRate® HD is a 0.635 mm pitch, multi-row interconnect system that provides an ultra-high density interface and

The ADM6, ADF6 Series has up to 400 total I/Os in a mere 1.88 square inches (12.1 square cm) of PCB real estate. This is possible due to the interconnect’s four rows of pins, on 0.635 mm pitch with up to 60 pins per row and a slim 5 mm wide insulator footprint. The mated stack height is a low 5 mm, with 7 mm and 10 mm stack heights to follow.

The system incorporates the Edge Rate® contact system, which is optimized for signal integrity performance. It is rated to 56 Gbps with PAM4 modulation.

Solder ball technology, for simplified processing, is standard, as are alignment pins and body polarization. The products are RoHS compliant and lead-free solderable.

For more information go to samtec.com/acceleratehd.

Samtec Flyover™ Quad Small Form Factor Pluggable Double Density: Samtec’s New FQSFP-DD

Samtec was the first interconnect company to bring the QSFP Flyover product line to market. Samtec is excited to announce another first in the Flyover realm: Samtec’s FQSFP-DD is the first product to take the Samtec Flyover™ architecture concept to the QSFP-DD form factor.

The QSFP-DD form factor focuses on a next generation high-density, high-speed pluggable backwards compatible module form factor. The FQSFP-DD Samtec Flyover™ product meets this challenge with greater performance margin compared to the QSFP-DD connector-to-PCB approach. As advanced 50+ Gbps per channel ASIC and FPGA solutions hit the market, the next-generation Samtec Flyover approach overcomes the limitations of signal loss on a PCB trace and continues to become more relevant.

QSFP-DD pluggable modules support double the aggregate bandwidth of conventional QSFP modules by adding a second row of contacts which enable support for a 16 differential pair electrical interface (aggregate 200 Gbps NRZ or 400 Gbps PAM4). Systems designed for QSFP-DD modules will be backwards compatible with existing QSFP plug-in modules and provide increased flexibility for end users, network platform designers and integrators.

The Samtec Flyover QSFP system provides improved signal integrity and architectural flexibility by removing critical high-speed signals from lossy PCB materials and transferring directly to the panel via ultra-low skew twinax cable. Double density Samtec Flyover increases throughput over QSFP by adding a second row of contacts enabling support for an eight-lane electrical interface. This is the FQSFP -DD Series.

For more information go to samtec.com/qsfp-flyover.

Featured Events and Demos

Wednesday, January 30, 2019 | 4:00pm| Booth #737

Product Showcase: Samtec 56 Gbps 7m ExaMAX® Backplane Cable Demonstration

Long-reach chip-to-chip demonstration using eSilicon SERDES and featuring Samtec’s 56 Gbps 7 m ExaMAX® backplane cable assembly with nearly

Thursday, January 31, 2019 | 2:00pm| Xilinx – Booth #737

Product Showcase: Samtec 112 Gbps PAM4 Flyover Cable Solution

In-booth demonstration partnered with Xilinx to exhibit long reach SERDES generating

Thursday, January 31, 2019 | 4:00pm| Booth #737

Product Showcase: Samtec 56 Gbps PAM4 Active Product Demonstrator

An in-booth demonstration of 56 Gbps PAM4 based systems that are fully realizable today with Samtec Flyover™ and High-Speed Interconnects.

Presentations

Tuesday, January 29, 2019 | 9:00am – 12:00pm

A Practical Guide to Channel Operating Margin (COM) & Effective Return Loss (ERL) Measurements

Presenter: Richard Mellitz – Distinguished Engineer, Samtec

Audience Level: All

Session Type: Tutorial

Room: Ballroom C

Track Name: 13 – Applying Test & Measurement Methodology

Description: COM and ERL Measurements have become common in the high-speed Ethernet standards and will soon be appearing in new computer bus standards such as PCIe. While these are important tools for the system designer, many do not fully understand them. This session, taught by some of the originators of these measurements, digs deep into the elements of the computation, and how they relate to the actual system. Practical methods of performing the measurements which supply the required parameters will be covered, along with practical methods of measurement system de-embed.

Tuesday, January 29, 2019 | 4:45pm – 6:00pm

Presenter: Richard Mellitz – Distinguished Engineer, Samtec

Audience Level: All

Session Type: Panel Discussion

Room: Ballroom G

Track Name: 05 – Advances in Materials & Processing for PCBs, Modules & Packages

Description: 100Gbps Ethernet (IEEE 802.3ck) and OIF CEI 112Gbps specifications have pushed the Nyquist frequencies to 26.56GHz and 28GHz. This means that device and system vendors need to re-evaluate their bandwidth requirements and link configurations such as: reduction of channel budget due to extra insertion loss consumed by packages, device/package/PCB co-optimizations, package impedance choices, and consideration of package’s PVT variations. In this panel, we would like to discuss the impacts, challenges, technology outlook, and solutions with experts from various areas including device/package design, standards, test and measurement, system builders, and 3D EM modeling.

Wednesday, January 30, 2019 | 9:00am – 9:45am

Presenters: Gustavo Blando, Istvan Novak, Scott McMorrow – Samtec

Audience Level: Introductory

Session Type: Technical Session

Room: Ballroom D

Track Name: 14 – Modeling & Analysis of Interconnects

Description: High frequency losses, crosstalk, impedance discontinuities, DC losses etc. are some of the physical phenomena that make us, SI/PI engineers spend most of our time. The slanted etch characteristics of traces called etch factor, affects all the above. This study will show how important or not is this effect for different types of applications. With the objective to provide simple guidelines to the practitioner engineer, we’ll look at many cases where the etch factor plays a role, ranging from the effect on traces at high speed, to the effect on heavily perforated planes at DC for current distribution.

Wednesday, January 30, 2019 | 9:00am – 9:45am

Case Studies Isolating Types of Power-Integrity Effects on Signal-Integrity & Means of Mitigation

Presenter: Rula Bakleh – SI/PI Expert, Samtec Teraspeed Consulting

Audience Level: Intermediate

Session Type: Technical Session

Room: Ballroom F

Track Name: 02 – Chip I/O & Functional Block Modeling & Validation Solutions

Description: The interaction between power and signal integrity is often complicated and confusing. With the single-ended DDR5 bus reaching the same data rates as many popular differential SerDes channels, a better understanding of this interaction becomes more crucial. In this paper, we discuss the three primary methods that power and signal integrity interact with each other and present multiple cases that demonstrate situations where such interactions occur, with a focus on the impact on DDR5.

Wednesday, January 30, 2019 | 9:00am – 9:45am

Effect of Power Plane Inductance on Power Delivery Networks

Presenter: Istvan Novak – Principle Signal and Power Integrity Engineer, Samtec

Audience Level: All

Session Type: Technical Session

Room: Ballroom E

Track: 11 – Power Integrity in Power Distribution Networks

Description: Power plane loop inductance is an important metric in Power Delivery Network (PDN) design, but it is not easy to visualize how PCB design changes impact a power plane’s loop inductance. This paper considers the impact on loop inductance of common power plane design changes such as the placement of vias, the anti-pad pitch and periodicity in a pin field array, and the placement of decoupling capacitors. The analysis considers tradeoffs of parametric values and provides guidance to engineers for PDN designs that meet a desired frequency response, minimize ground bounce, and reduce coupling due to power plane loop inductance.

Wednesday, January 30, 2019 | 11:00am – 11:45am

Presenter: Jim Nadolny – Engineering Manager, Samtec

Audience Level: All

Session Type: Technical Session

Room: Ballroom D

Track Name: 13 – Applying Test & Measurement Methodology

Description: S-parameter measurement and fixture de-embedding are critical tasks especially when measurements and models are shared across multiple teams. In this session, we will present a review of best practices for VNA measurements and fixture de-embedding. We will also present the results of a study performed in the context of the IEEE P370 standard analyzing the variation of results across multiple teams for the measurement and fixture de-embedding of the same set of PCB test coupons.

Wednesday, January 30, 2019 | 3:45pm – 5:00pm

PCI Express® Ecosystem: Getting Ready for 32 GT/s

Presenter: Steve Krooswyk – New Connector SI Design, Samtec

Audience Level: All

Session Type: Panel Discussion

Room: Ballroom C

Track Name: 08 – Optimizing High-Speed Serial Design

Description: The PCI Express ecosystem will soon make a generational leap, doubling to 32GT/s. Our panel highlights the challenges in designing, implementing, and validating a new generation of PCI Express. We review the critical silicon to silicon questions: Is Gen5 PHY destined to use more DFE and more power? How to navigate controller and switch options? How do I know a cable or connector is 32G capable? What scope BW is required? Is the package more important at 32G? What channel optimization is needed? What potential add in card improvements?

Thursday, January 31, 2019 | 8:00am – 8:45am

Practical Implementation of Testing 50 Gbps per Lane Effective Return Loss (ERL)

Presenter: Richard Mellitz – Distinguished Engineer, Samtec

Audience Level: Intermediate

Session Type: Technical Session

Room: Ballroom C

Track Name: 13 – Applying Test & Measurement Methodology

Description: The paper is to provide a detailed analysis of the relationship between the return loss of the channel, its components, and the channel operating margin (COM) results supporting the introduction of effective return loss (ERL) for the IEEE 802.3cd 50 Gb/s lane standard. ERL is characterized as a figure of merit for the electromagnetic wave reflection from a device or a channel input or output. It is calculated using the method described in the draft standard. The paper will provide practical examples of implementing the ERL method for transmitters, receivers, and cable assemblies by measurements of their scattering parameters.

Thursday, January 31, 2019 | 11:00am – 11:45am

How the Braid Impedance of Instrumentation Cables Impact PI & SI Measurements

Presenter: Istvan Novak, Jim Nadolny, Gary Biddle – Samtec

Audience Level: Intermediate

Session Type: Technical Session

Room: Ballroom G

Track Name: 13 – Applying Test &Measurement Methodology

Description: VNA instrumentation cables have a direct impact on low frequency, high dynamic range measurements. In this paper, we explain this phenomenon in the context of power integrity measurements. DC resistance and low frequency transfer impedance are relevant cable metrics which are shown to correlate with the measurement dynamic range.

Thursday, January 31, 2019 | 2:00pm – 2:40pm

Don’t Judge a Bit Just By It’s Fourier – 112 Gbps PAM4 Component Optimization & Selection

Presenter: Steve Krooswyk, Madhumitha Rengarajan – Samtec

Audience Level: All

Session Type: Technical Session

Room: Ballroom B

Track: 08 – Optimizing High-Speed Serial Design

Description: With a new generation of “56-112 Gbps components” of varying performance levels coming to the market, distinction and selection are increasingly important yet very difficult. Categorizing components using traditional frequency domain responses does not always correlate to channel performance, as the channel takes a holistic time-domain simulation approach to compliance. This paper explores data-rate and spectral content dependent component evaluation that is sensitive to the nuances important to channel performance. Using component level Effective Return Loss (ERL), Integrated Crosstalk Noise (ICN) and their interaction, a diverse set of components are evaluated and quantitatively correlated to the respective 56-112 Gbps channel performances.

Passes

Register for your free VIP Expo Pass, and use our Promo Code:

Learn more about DesignCon 2019.